Section 16 Renesas Serial Peripheral Interface

R01UH0134EJ0400 Rev. 4.00 Page 845 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

(g) Transfer Operation Flowchart (CPHA = 1)

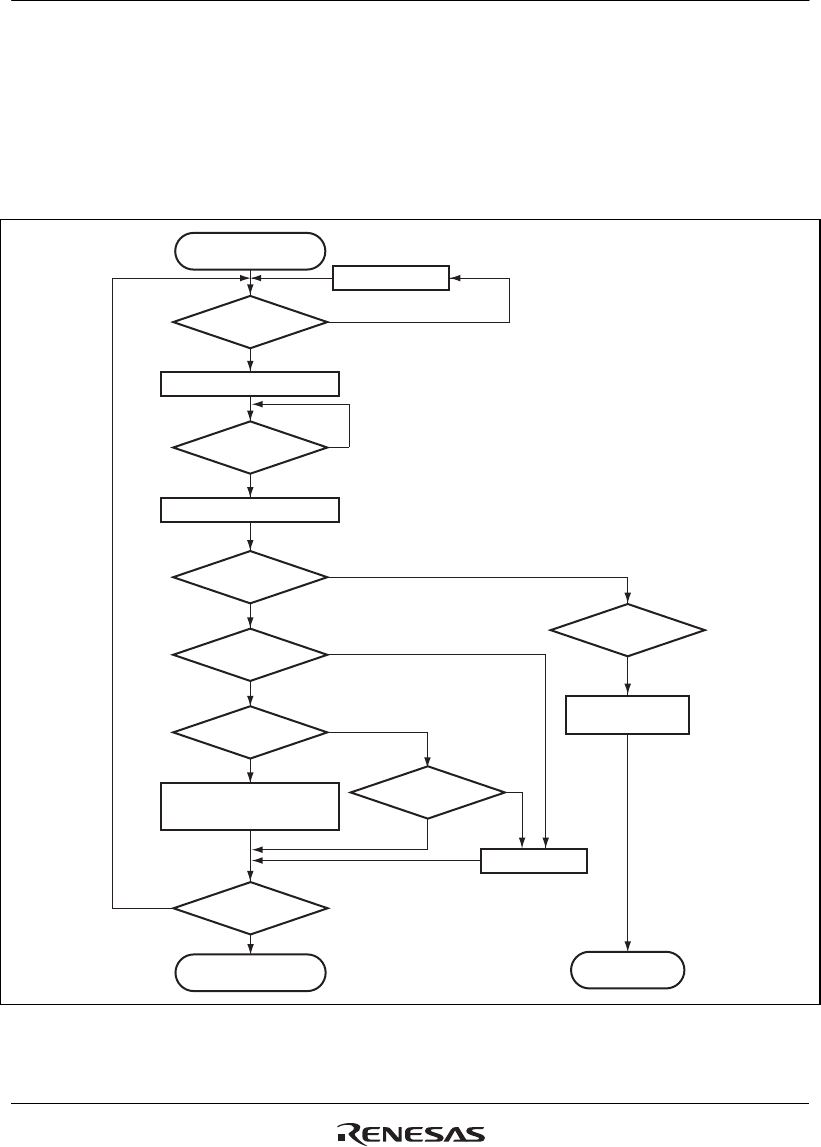

Figure 16.21 is a flowchart illustrating a transfer in SPI operation when this module is used in

slave mode with the CPHA bit in the command register 0 (SPCMD0) and the MODFEN bit in the

control register (SPCR) set to 1, respectively. The subsequent operation is not guaranteed when

the serial transfer is started with the MODFEN bit set to 0 and the SSL input level is negated with

the number of RSPCK cycles shorter than the data length.

End of transfer

No

Yes

Error handling

Error

occurred

Copy received data from the

shift register to the receive

buffer

Detect mode

fault error

RSPCK cycle count

RSPCK input level

Receive buffer

status

Overrun error

status

SSL input level

Negate

Empty

Error occurred

No error

Full

No change

Changed

No error

Shorter than data length

Equal to data length

Start serial transfer

MISO output

SSL input level

MISO Hi-Z

Negate

Assert

End of initialization

in slave mode

Overrun error

status

Error handling

Continue data

transfer

Figure 16.21 Transfer Operation Flowchart in Slave Mode (CPHA = 1)