Section 25 NAND Flash Memory Controller

Page 1306 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

25.3.8 Interrupt DMA Control Register (FLINTDMACR)

FLINTDMACR is a 32-bit readable/writable register that enables or disables DMA transfer

requests or interrupts. A transfer request from this module to the direct memory access controller

is issued after each access mode has been started.

Bits 9 to 5 are the flag bits that indicate various errors occurred in flash memory access and

whether there is a transfer request from the FIFO. Only 0 can be written to these bits. To clear a

flag, write 0 to the target flag bit and 1 to the other flag bits.

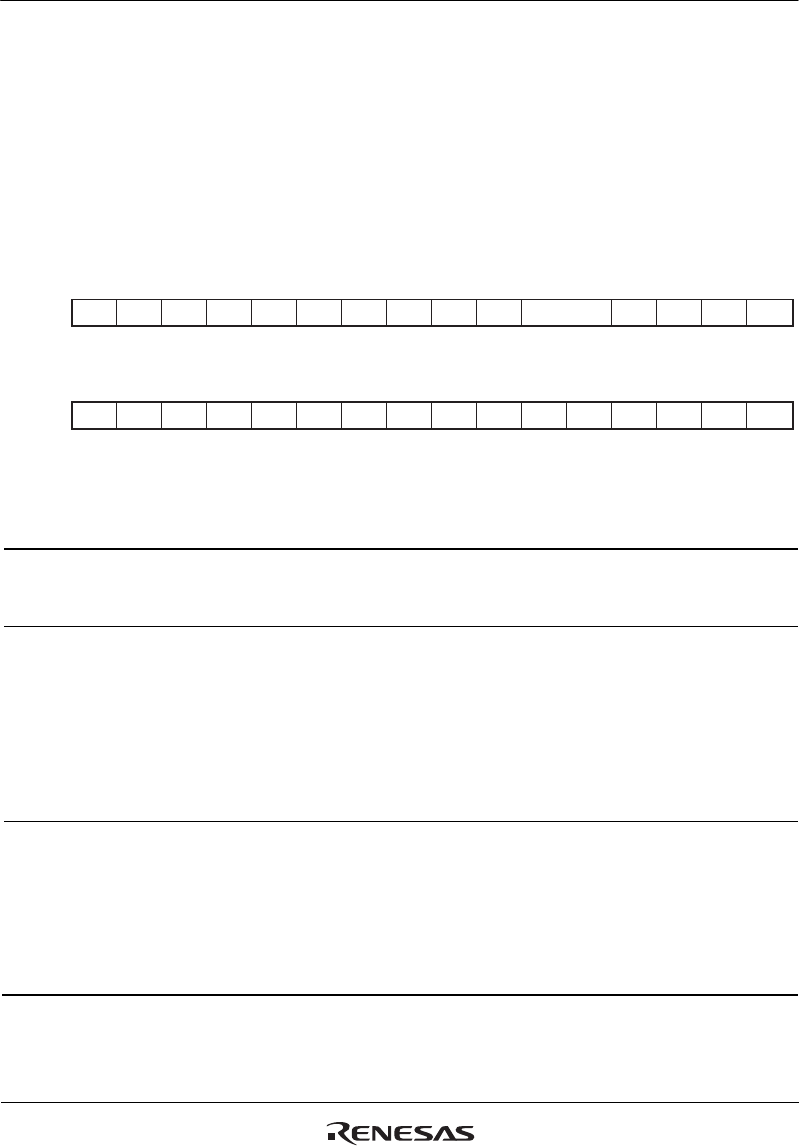

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

151413121110987654321

0

0000000000000000

RRRRRRRR/WRRR/WR/WR/WR/WR/WR/W

0000000000000000

RRRRRRR/(W)*R/(W)*R/(W)*R/(W)*R/(W)* R/W R/W R/W R/W R/W

------

4ECE

INTE

ECER

INTE

--

FIFOTRG

[1:0]

AC1

CLR

AC0

CLR

DREQ1

EN

DREQ0

EN

------

EC

ERB

ST

ERB

BTO

ERB

TRR

EQF1

TRR

EQF0

STER

INTE

RBER

INTE

TE

INTE

TR

INTE1

TR

INTE0

Bit Bit Name

Initial

Value R/W Description

31 to 26 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

25 4ECEINTE 0 R/W 4-Symbol ECC Pattern Generation End Interrupt

Enable

Enables or disables an interrupt to CPU by 4-symbol

ECC pattern generation end.

0: Disables an interrupt to CPU by 4-symbol ECC

pattern generation end.

1: Enables an interrupt to CPU by 4-symbol ECC

pattern generation end.

24 ECERINTE 0 R/W ECC Error Interrupt Enable

Enables or disables an interrupt to CPU when ECC

error occurs.

0: Disables an interrupt to CPU when an ECC error

occurs

1: Enables an interrupt to CPU when an ECC error

occurs