Section 2 CPU

R01UH0134EJ0400 Rev. 4.00 Page 85 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

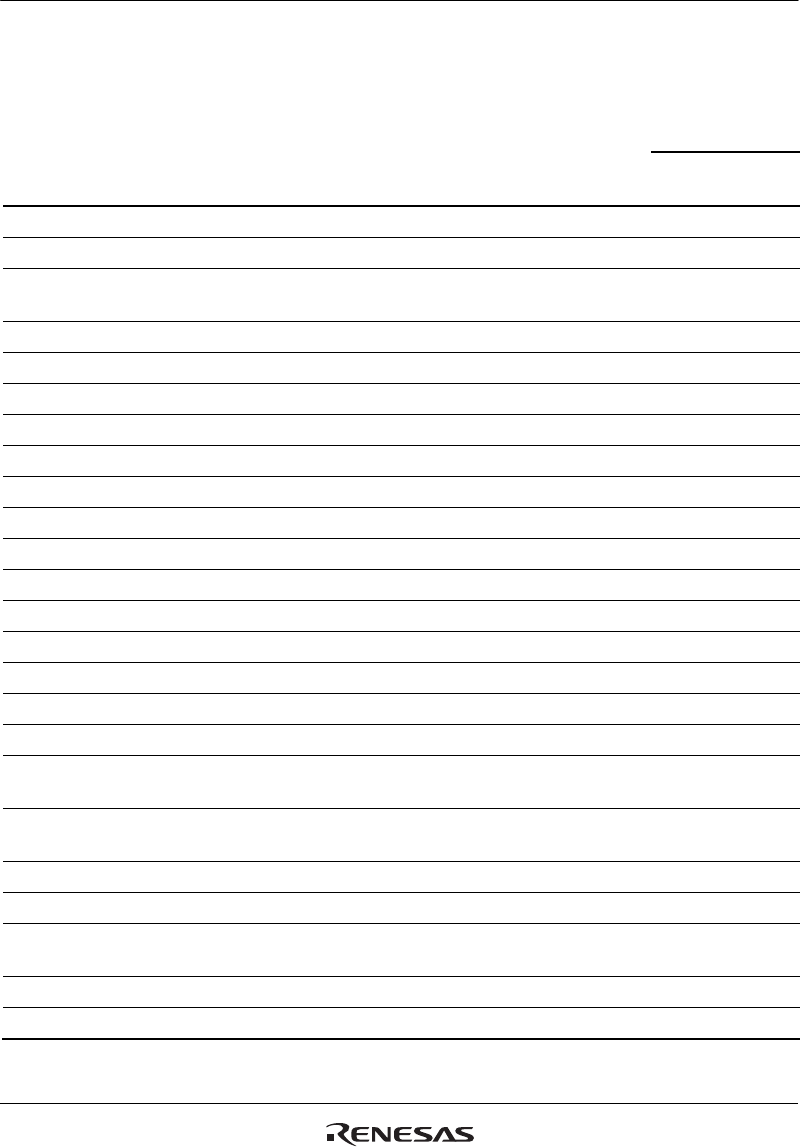

2.4.7 System Control Instructions

Table 2.16 System Control Instructions

Instruction Instruction Code Operation

Execu-

tion

Cycles

T Bit

Compatibility

SH2,

SH2E

SH4 SH-2A

CLRT 0000000000001000 0 T 1 0 Yes Yes Yes

CLRMAC 0000000000101000 0 MACH,MACL 1 Yes Yes Yes

LDBANK @Rm,R0 0100mmmm11100101 (Specified register bank entry)

R0

6 Yes

LDC Rm,SR 0100mmmm00001110 Rm SR 3 LSB Yes Yes Yes

LDC Rm,TBR 0100mmmm01001010 Rm TBR 1 Yes

LDC Rm,GBR 0100mmmm00011110 Rm GBR 1 Yes Yes Yes

LDC Rm,VBR 0100mmmm00101110 Rm VBR 1 Yes Yes Yes

LDC.L @Rm+,SR 0100mmmm00000111 (Rm) SR, Rm + 4 Rm 5 LSB Yes Yes Yes

LDC.L @Rm+,GBR 0100mmmm00010111 (Rm) GBR, Rm + 4 Rm 1 Yes Yes Yes

LDC.L @Rm+,VBR 0100mmmm00100111 (Rm) VBR, Rm + 4 Rm 1 Yes Yes Yes

LDS Rm,MACH 0100mmmm00001010 Rm MACH 1 Yes Yes Yes

LDS Rm,MACL 0100mmmm00011010 Rm MACL 1 Yes Yes Yes

LDS Rm,PR 0100mmmm00101010 Rm PR 1 Yes Yes Yes

LDS.L @Rm+,MACH 0100mmmm00000110 (Rm) MACH, Rm + 4 Rm 1 Yes Yes Yes

LDS.L @Rm+,MACL 0100mmmm00010110 (Rm) MACL, Rm + 4 Rm 1 Yes Yes Yes

LDS.L @Rm+,PR 0100mmmm00100110 (Rm) PR, Rm + 4 Rm 1 Yes Yes Yes

NOP 0000000000001001 No operation 1 Yes Yes Yes

RESBANK 0000000001011011 Bank R0 to R14, GBR,

MACH, MACL, PR

9* Yes

RTE 0000000000101011 Delayed branch,

stack area PC/SR

6 Yes Yes Yes

SETT 0000000000011000 1 T 1 1 Yes Yes Yes

SLEEP 0000000000011011 Sleep 5 Yes Yes Yes

STBANK R0,@Rn 0100nnnn11100001 R0

(specified register bank entry)

7 Yes

STC SR,Rn 0000nnnn00000010 SR Rn 2 Yes Yes Yes

STC TBR,Rn 0000nnnn01001010 TBR Rn 1 Yes