Section 26 USB 2.0 Host/Function Module

R01UH0134EJ0400 Rev. 4.00 Page 1373 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

(2) D0FIFOSEL, D1FIFOSEL

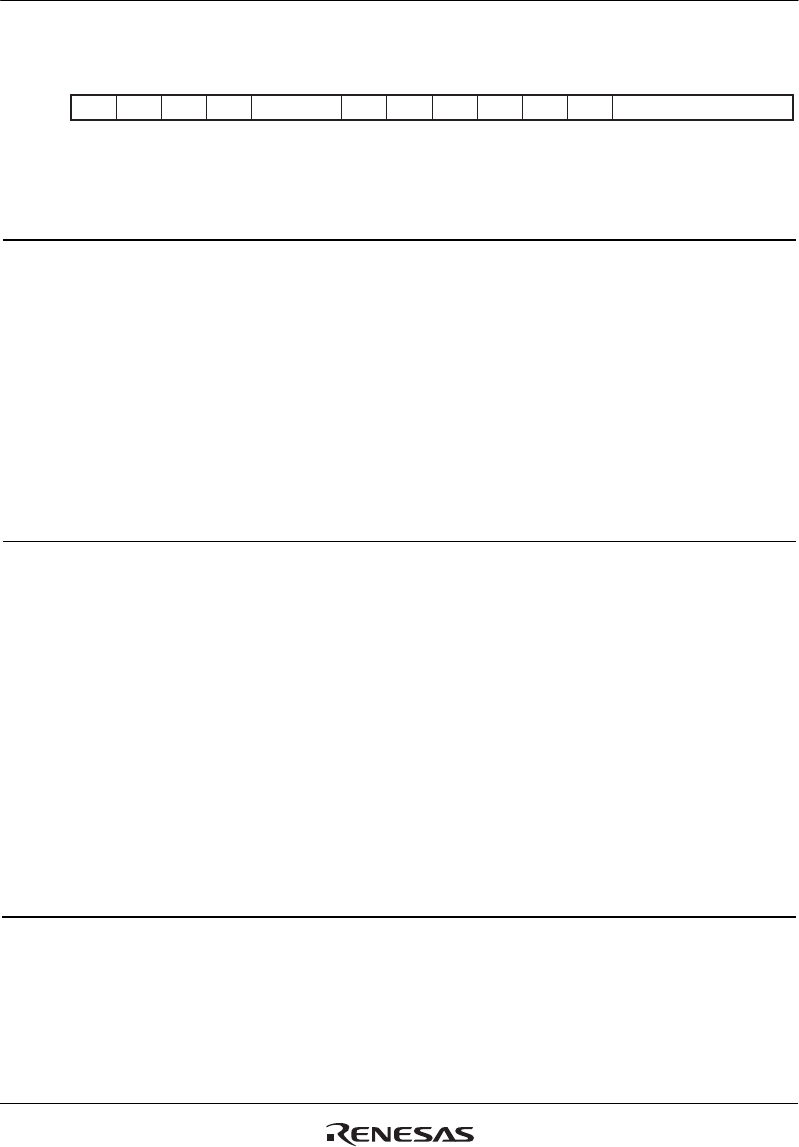

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Bit:

Initial value:

R/W:

0000000000000000

R/W R/W* R/W R/W R/W R/W R R/W R R R R R/W R/W R/W R/W

RCNT REW DCLRM DREQE MBW[1:0]

BIG

END

— — — CURPIPE[3:0]

—

—

Bit Bit Name

Initial

Value R/W Description

15 RCNT 0 R/W Read Count Mode

Specifies the read mode for the value in the DTLN

bits in DnFIFOCTR.

0: The DTLN bit is cleared when all of the receive

data has been read from the DnFIFO.

(In double buffer mode, the DTLN bit value is

cleared when all the data has been read from a

single plane.)

1: The DTLN bit is decremented when the receive

data is read from the DnFIFO.

When accessing DnFIFO with the BFRE bit set to 1,

set this bit to 0.

14 REW 0 R/W* Buffer Pointer Rewind

Specifies whether or not to rewind the buffer pointer.

0: The buffer pointer is not rewound.

1: The buffer pointer is rewound.

When the selected pipe is in the receiving direction,

setting this bit to 1 while the FIFO buffer is being

read allows re-reading the FIFO buffer from the first

data (in double buffer mode, re-reading the currently-

read FIFO buffer plane from the first data is allowed).

Do not set REW to 1 simultaneously with modifying

the CURPIPE bits. Before setting REW to 1, be sure

to check that FRDY is 1.

To re-write to the FIFO buffer again from the first

data for the pipe in the transmitting direction, use the

BCLR bit.