R01UH0134EJ0400 Rev. 4.00 Page 2087 of 2108

Sep 24, 2014

Item Page Revision (See Manual for Details)

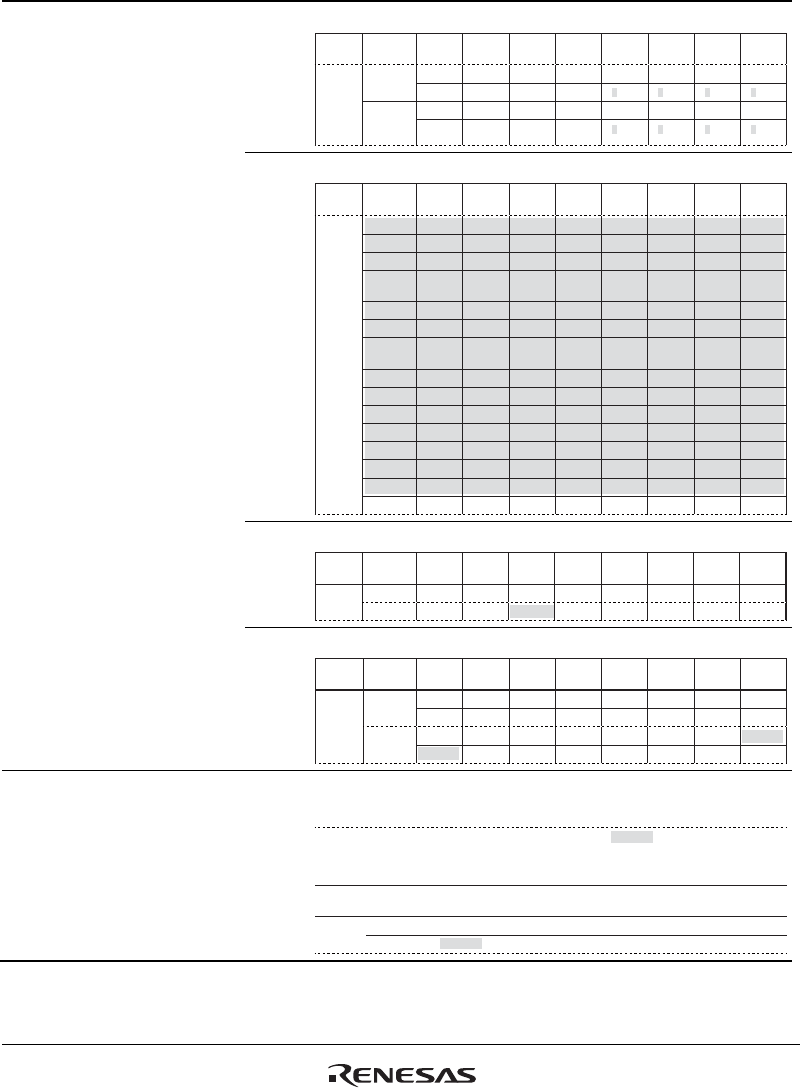

36.2 Register Bits 1926 Table amended

Module Name

Register

Abbreviation

Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

Controller area

network

MBn_CONTROL

1_1(n = 0)

⎯ ⎯ NMC ⎯ ⎯ MBC[2] MBC[1] MBC[0]

⎯ ⎯ ⎯ ⎯ DLC[3] DLC[2] DLC[1] DLC[0]

MBn_CONTROL

1_1

(n = 0 to 31)

⎯ ⎯ NMC ATX DART MBC[2] MBC[1] MBC[0]

⎯ ⎯ ⎯ ⎯ DLC[3] DLC[2] DLC[1] DLC[0]

1929 Table amended

Module Name

Register

Abbreviation

Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

CD-ROM

decoder

CROMEN SUBC_EN CROM_EN CROM_STP ⎯ ⎯ ⎯ ⎯ ⎯

CROMSY0 SY_AUT SY_IEN SY_DEN ⎯ ⎯ ⎯ ⎯ ⎯

CROMCTL0 MD_DESC ⎯ MD_AUTO MD_AUTOS1 MD_AUTOS2 MD_SEC[2] MD_SEC[1] MD_SEC[0]

CROMCTL1 M2F2EDC MD_DEC[2] MD_DEC[1] MD_DEC[0] ⎯ ⎯

MD_

PQREP[1]

MD_

PQREP[0]

CROMCTL3 STP_ECC STP_EDC ⎯ STP_MD STP_MIN ⎯ ⎯ ⎯

CROMCTL4 ⎯ LINK2 ⎯ EROSEL NO_ECC ⎯ ⎯ ⎯

CROMCTL5 ⎯ ⎯ ⎯ ⎯ ⎯ ⎯ MSF_LBA_

SEL

CROMST0 ⎯ ⎯ ST_SYIL ST_SYNO ST_BLKS ST_BLKL ST_SECS ST_SECL

CROMST1 ⎯ ⎯ ⎯ ⎯ ER2_HEAD0 ER2_HEAD1 ER2_HEAD2 ER2_HEAD3

CROMST3

ER2_SHEAD0 ER2_SHEAD1 ER2_SHEAD2 ER2_SHEAD3 ER2_SHEAD4 ER2_SHEAD5 ER2_SHEAD6 ER2_SHEAD7

CROMST4 NG_MD NG_MDCMP1 NG_MDCMP2 NG_MDCMP3 NG_MDCMP4 NG_MDDEF NG_MDTIM1 NG_MDTIM2

CROMST5 ST_AMD[2] ST_AMD[1] ST_AMD[0] ST_MDX LINK_ON LINK_DET LINK_SDET LINK_OUT1

CROMST6 ST_ERR ⎯ ST_ECCABT ST_ECCNG ST_ECCP ST_ECCQ ST_EDC1 ST_EDC2

CBUFST0 BUF_REF BUF_ACT ⎯ ⎯ ⎯ ⎯ ⎯ ⎯

CBUFST1 BUF_ECC BUF_EDC ⎯ BUF_MD BUF_MIN ⎯ ⎯ ⎯

1930 Table amended

Module Name

Register

Abbreviation

Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

CD-ROM

decoder

SHEAD00 SHEAD00[7] SHEAD00[6] SHEAD00[5] SHEAD00[4] SHEAD00[3] SHEAD00[2] SHEAD00[1] SHEAD00[0]

CBUFCTL0 CBUF_AUT CBUF_EN ⎯ CBUF_MD[1] CBUF_MD[0] CBUF_TS CBUF_Q ⎯

1937 Table amended

Module Name

Register

Abbreviation

Bit 31/23/15/7 Bit 30/22/14/6 Bit 29/21/13/5 Bit 28/20/12/4 Bit 27/19/11/3 Bit 26/18/10/2 Bit 25/17/9/1 Bit 24/16/8/0

USB 2.0

host/function

module

INTSTS0 VBINT RESM SOFR DVST CTRT BEMP NRDY BRDY

VBSTS DVSQ[2] DVSQ[1] DVSQ[0] VALID CTSQ[2] CTSQ[1] CTSQ[0]

DCPCFG ⎯ ⎯ ⎯ ⎯ ⎯ ⎯ ⎯ CNTMD

SHTNAK ⎯ ⎯ DIR ⎯ ⎯ ⎯ ⎯

36.3 Register States in

Each Operating Mode

1957 Table amended

Module

Name

Register

Abbreviation

Power-On

Reset

Manual

Reset

Deep

Standby

Software

Standby

Module

Standby

Sleep

Multi-

function

timer pulse

unit 2

All registers Initialized Retained Initialized Retained Initialized Retained

Compare

match timer

All registers Initialized Retained Initialized Initialized Retained Retained

Watchdog

timer

WRCSR Initialized*

1

Retained Initialized Retained

⎯

Retained

Other than abov e Initialized Initialized Initialized Retained

⎯

Retained