Section 16 Renesas Serial Peripheral Interface

Page 836 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

If the SSL signal settings in the SPCMD in which 1 is assigned to the SSLKP bit are different

from the SSL signal output settings in the SPCMD to be used in the next transfer, this module

switches the SSL signal status to SSL signal assertion ((5) in figure 16.16) corresponding to the

command for the next transfer. Notice that if such an SSL signal switching occurs, the slaves that

drive the MISO signal compete, and the possibility arises of the collision of signal levels.

This module in master mode references within the module the SSL signal operation for the case

where the SSLKP bit is not used. Even when the CPHA bit in SPCMD is 0, this module can

accurately start serial transfers by asserting the SSL signal for the next transfer. For this reason,

burst transfers in master mode can be executed irrespective of CPHA bit settings (see section

16.4.8 (2), Slave Mode Operation).

(e) RSPCK Delay (t1)

The RSPCK delay value in master mode depends on SCKDEN bit settings in the command

register (SPCMD) and on clock delay register (SPCKD) settings. This module determines the

SPCMD to be referenced during serial transfer by pointer control, and determines an RSPCK

delay value during serial transfer by using the SCKDEN bit in the selected SPCMD and SPCKD,

as shown in table 16.8. For a definition of RSPCK delay, see section 16.4.4, Transfer Format.

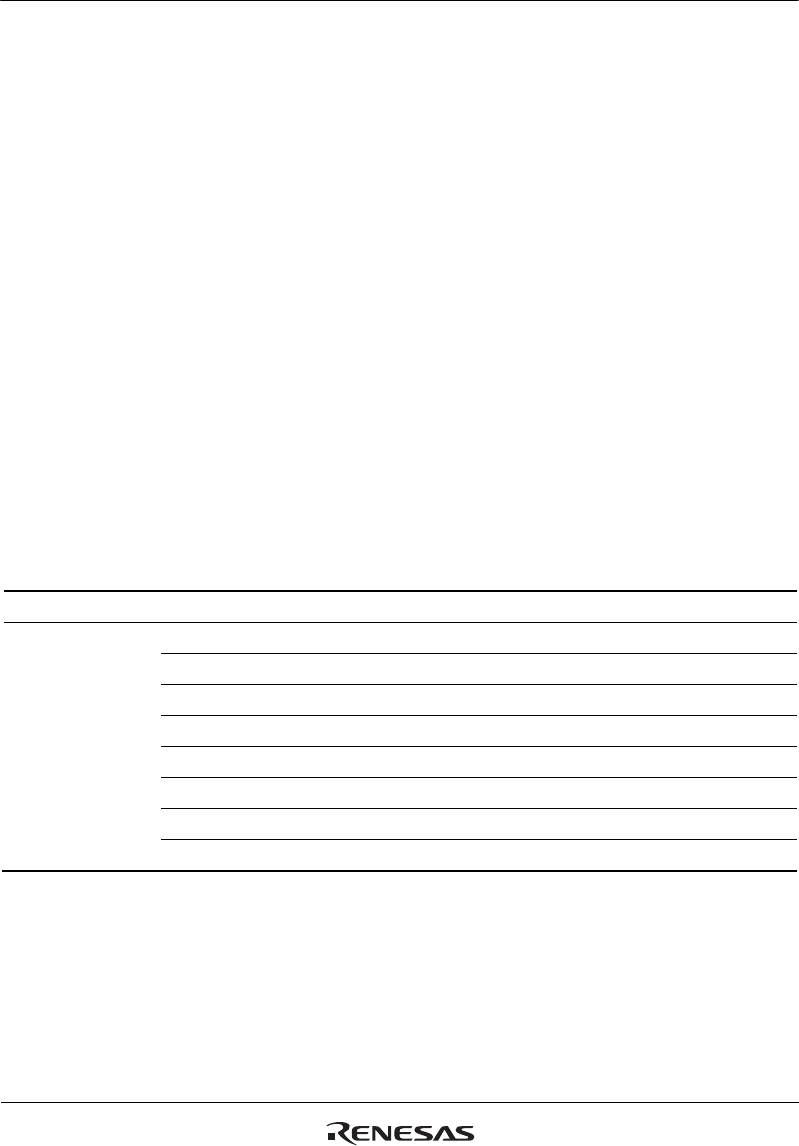

Table 16.8 Relationship among SCKDEN and SPCKD Settings and RSPCK Delay Values

SCKDEN SPCKD RSPCK Delay Value

0 000 to 111 1 RSPCK

1 000 1 RSPCK

001 2 RSPCK

010 3 RSPCK

011 4 RSPCK

100 5 RSPCK

101 6 RSPCK

110 7 RSPCK

111 8 RSPCK