Section 26 USB 2.0 Host/Function Module

Page 1520 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

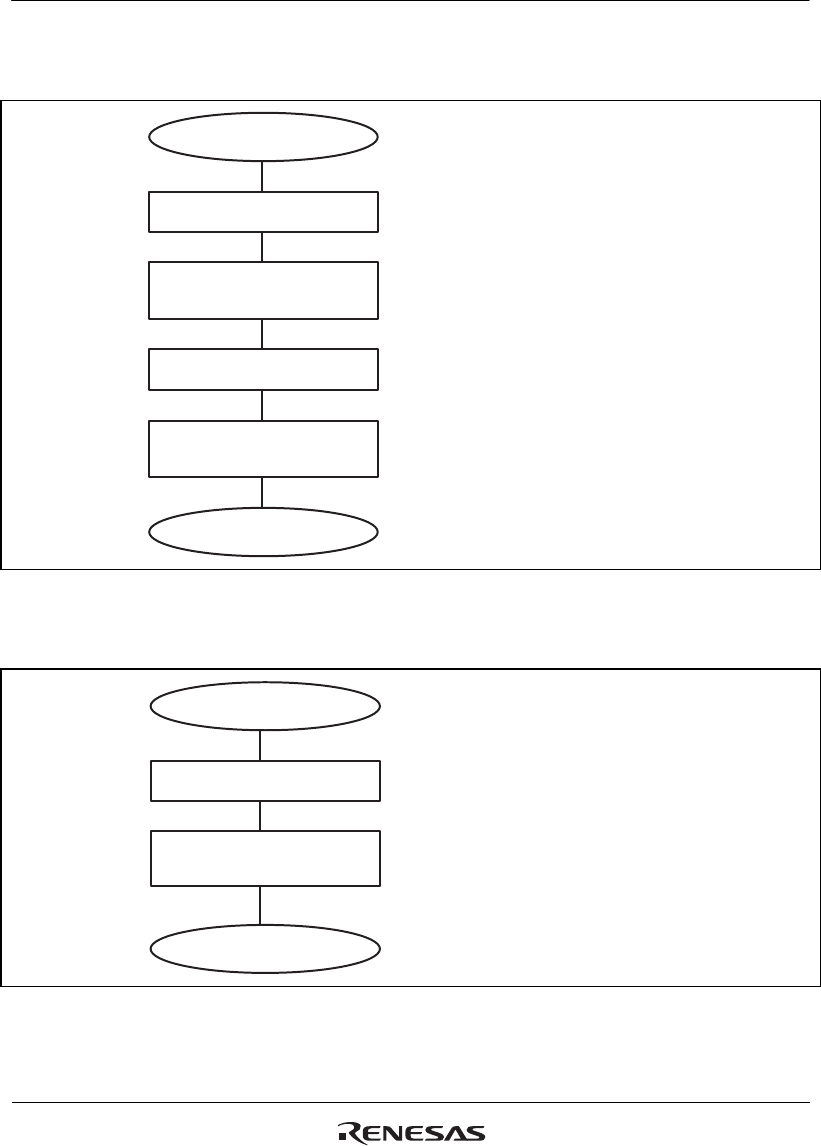

Example 1 for writing odd data: Writing data with 16-bit width once and then with 8-bit width

once

[1]

[2]

[3]

[4]

[1]

[2]

[3]

[4]

Start

Set MBW to 01.

Set MBW to 00.

Write 16-bit data to the FIFO

port register.

Write 8-bit data to the FIFO

port register.

Writing end

Set the FIFO port access width to 16 bits.

Write data to bits 31 to 16 when BIGEND = 1,

and bits 15 to 0 when BIGEND = 0.

Set the FIFO port access width to 8 bits.

Write data to bits 31 to 24 when BIGEND = 1,

and bits 7 to 0 when BIGEND = 0.

Figure 26.12 Example 1 for Writing Odd Data to FIFO Port

Example 1 for writing odd data 2: Writing data with 8-bit width three times

[1]

[2]

[1]

[2]

Set the FIFO port access width to 8 bits.

Write data to bits 31 to 24 when BIGEND = 1,

and bits 7 to 0 when BIGEND = 0.

Start

Writing end

Set MBW to 00.

Write 8-bit data to the FIFO

port register three times.

Figure 26.13 Example 2 for Writing Odd Data to FIFO Port