Section 15 Serial Communication Interface with FIFO

Page 766 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

Receiving Serial Data (Clock Synchronous Mode)

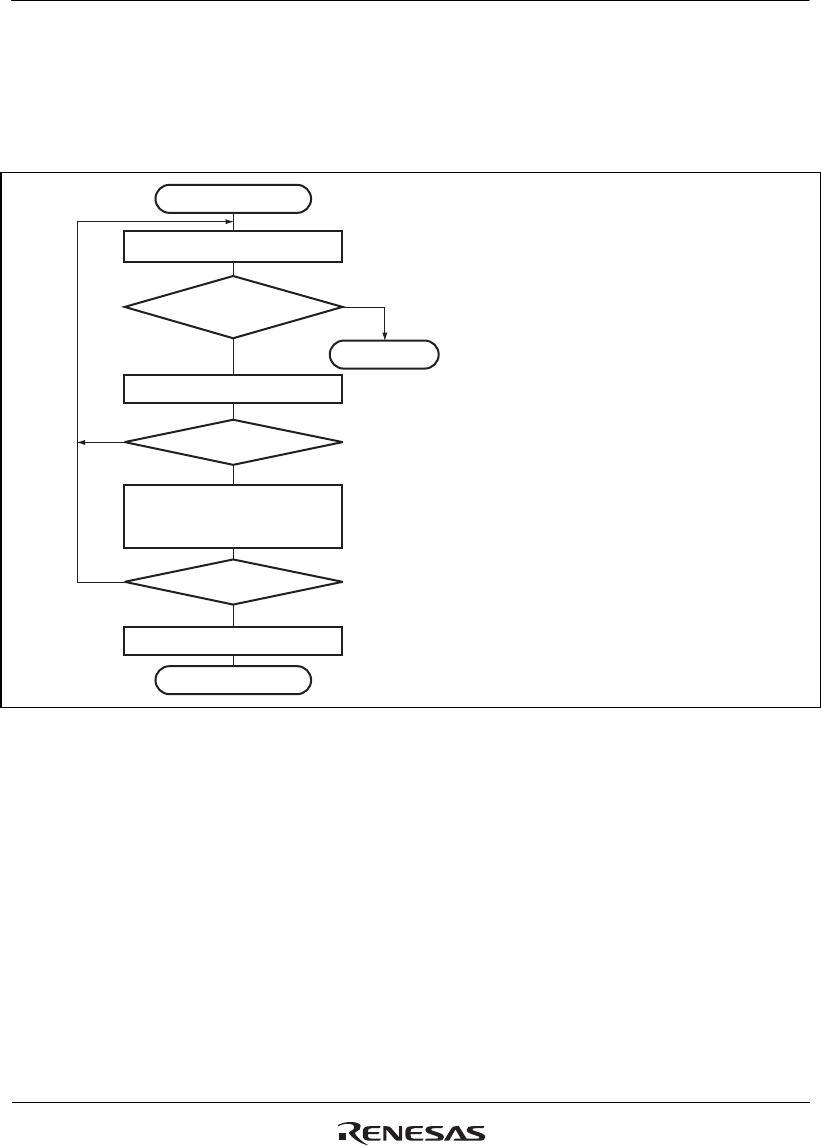

Figures 15.15 and 15.16 show sample flowcharts for receiving serial data. Use the following

procedure for serial data reception after enabling receive operation. When switching from

asynchronous mode to clock synchronous mode without initialization, make sure that ORER,

PER, and FER are cleared to 0.

Start of reception

Read ORER flag in SCLSR

ORER = 1?

Read RDF flag in SCFSR

RDF = 1?

Read receive data in

SCFRDR, and clear RDF

flag in SCFSR to 0

All data received?

Clear RE bit in SCSCR to 0

End of reception

Yes

No

Yes

Yes

No

No

Error handling

[1] Receive error handling:

Read the ORER flag in SCLSR to identify

any error, perform the appropriate error

handling, then clear the ORER flag to 0.

Reception cannot be resumed while the

ORER flag is set to 1.

[2] Status check and receive data read:

Read SCFSR and check that RDF = 1,

then read the receive data in SCFRDR,

and clear the RDF flag to 0. The transition

of the RDF flag from 0 to 1 can also be

identified by a receive FIFO data full

interrupt (RXI).

[3] Serial reception continuation procedure:

To continue serial reception, read at least

the receive trigger set number of receive

data bytes from SCFRDR, read 1 from the

RDF flag, then clear the RDF flag to 0.

The number of receive data bytes in

SCFRDR can be ascertained by reading

SCFRDR. However, the RDF bit is

cleared to 0 automatically when an RXI

interrupt activates the direct memory

access controller to read the data in

[1]

[2]

[3]

Figure 15.15 Sample Flowchart for Receiving Serial Data (1)