Section 10 Direct Memory Access Controller

R01UH0134EJ0400 Rev. 4.00 Page 385 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

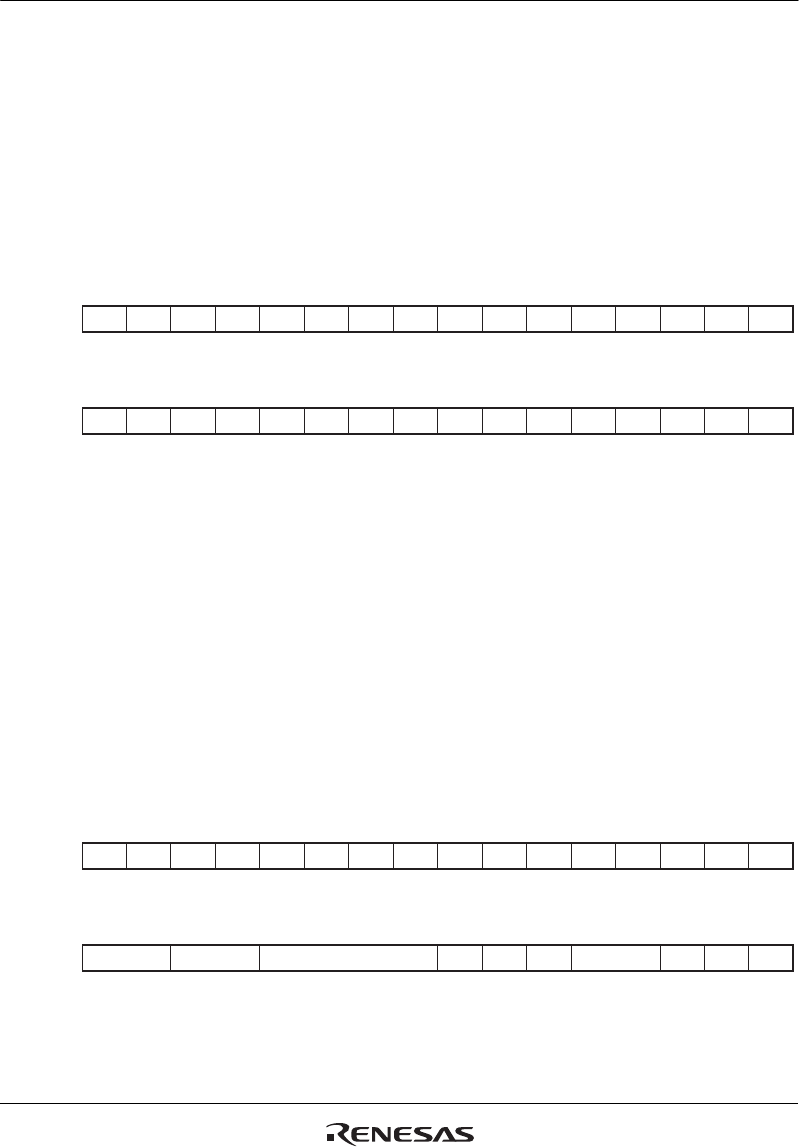

10.3.3 DMA Transfer Count Registers (DMATCR)

The DMA transfer count registers (DMATCR) are 32-bit readable/writable registers that specify

the number of DMA transfers. The transfer count is 1 when the setting is H'00000001, 16,777,215

when H'00FFFFFF is set, and 16,777,216 (the maximum) when H'00000000 is set. During a DMA

transfer, these registers indicate the remaining transfer count.

The upper eight bits of DMATCR are always read as 0, and the write value should always be 0. To

transfer data in 16 bytes, one 16-byte transfer (128 bits) counts one.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

R R R R R R R R R/W R/W R/W R/W R/W R/W R/W R/W

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

----------------

----------------

10.3.4 DMA Channel Control Registers (CHCR)

The DMA channel control registers (CHCR) are 32-bit readable/writable registers that control the

DMA transfer mode.

The DO, AM, AL, DL, DS, and TL bits which specify the DREQ, DACK, and TEND external pin

functions can be read and written to in channels 0 and 1*

1

, but they are reserved in channels 2 to

15*

2

.

Notes: 1. Only channel 0 can be used in the SH7262 Group.

2. Channels 1 to 15 can be used in the SH7262 Group.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

R/W R R/W R/W R R/W R/W R R/W R/W R R/W R/(W)* R/W R/W R/W

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/(W)* R/W

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

Note: Only 0 can be written to clear the flag after 1 is read.*

TC -

RLD

SAR

RLD

DAR

- DAF SAF - DO TL -

TE

MASK

HE HIE AM AL

DM[1:0] SM[1:0] RS[3:0] DL DS TB TS[1:0] IE TE DE