Section 26 USB 2.0 Host/Function Module

R01UH0134EJ0400 Rev. 4.00 Page 1523 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

condition as when BVAL = 1). Whether to sample the DMA transfer end signal can be specified

through the TENDE bit in DnFBCFG.

Note that this function cannot be used when the DMA transfer size is set to 16 bytes.

(c) DnFIFO Auto Clear Mode (D0FIFO/D1FIFO Port Reading Direction)

If 1 is set for the DCLRM bit in DnFIFOSEL, the module automatically clears the buffer memory

of the selected pipe when reading of the data from the buffer memory has been completed.

Table 26.25 shows the packet reception and buffer memory clearing processing for each of the

various settings. As shown, the buffer clear conditions depend on the value set to the BFRE bit.

Using the DCLRM bit eliminates the need for the buffer to be cleared even if a situation occurs

that necessitates clearing of the buffer. This makes it possible to carry out DMA transfers without

involving software.

This function can be set only in the buffer memory reading direction.

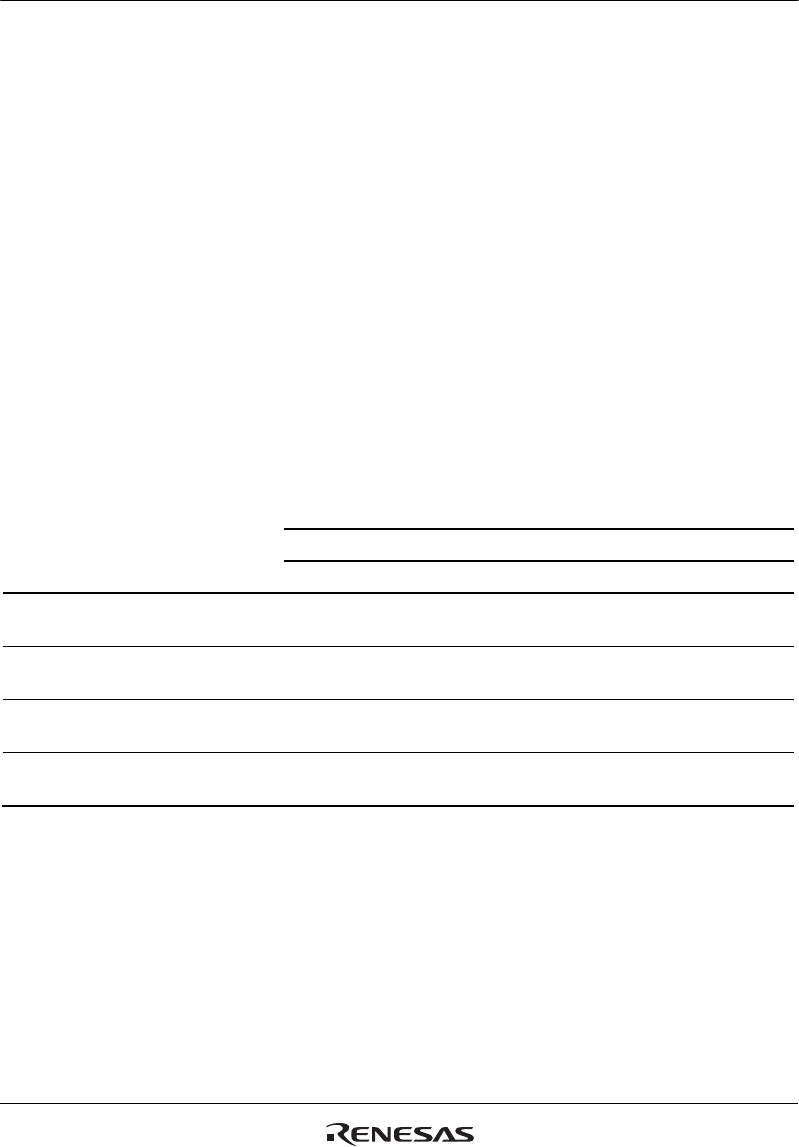

Table 26.25 Packet Reception and Buffer Memory Clearing Processing

Buffer Status

When Packet is Received

Register Setting

DCLRM 0 DCLRM 1

BFRE = 0 BFRE = 1 BFRE = 0 BFRE = 1

Buffer full Doesn't need

to be cleared

Doesn't need

to be cleared

Doesn't need

to be cleared

Doesn't need

to be cleared

Zero-length packet reception Needs to be

cleared

Needs to be

cleared

Doesn't need

to be cleared

Doesn't need

to be cleared

Normal short packet reception Doesn't need

to be cleared

Needs to be

cleared

Doesn't need

to be cleared

Doesn't need

to be cleared

Transaction count ended Doesn't need

to be cleared

Needs to be

cleared

Doesn't need

to be cleared

Doesn't need

to be cleared