Section 26 USB 2.0 Host/Function Module

R01UH0134EJ0400 Rev. 4.00 Page 1485 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

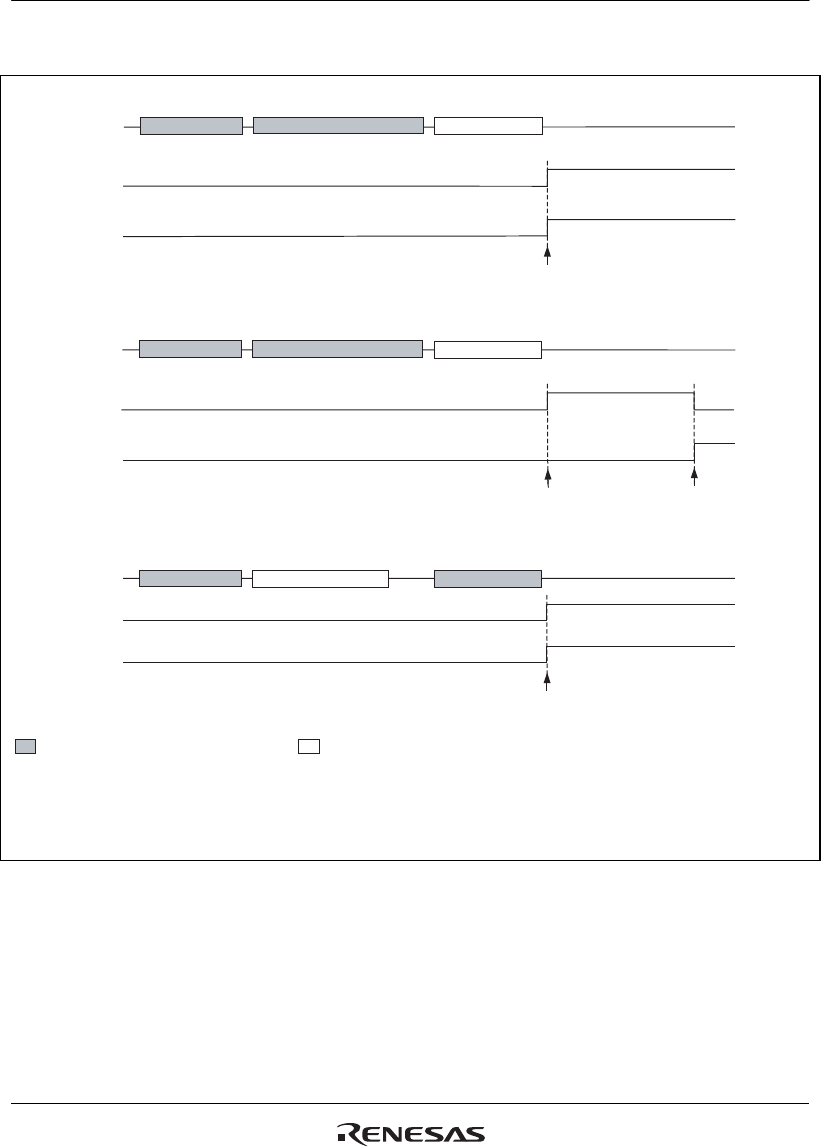

Figure 26.3 shows the timing at which the BRDY interrupt is generated.

Token Packet ACK Handshake

Token Packet

Token Packet

Data Packet ACK Handshake

<Last> Data Packet

Data Packet

ACK Handshake

(1) Zero-length packet reception or data packet reception when BFRE = 0 (in single buffer mode)

USB bus

FIFO buffer status

BRDY interrupt

(corresponding

PIPEBRDY bit is

changed)

A BRDY interrupt is generated

because reading from the buffer is enabled*2.

*1 In isochronous transfer, ACK Handshake is not transmitted.

*2 Reading the FIFO buffer is enabled when one packet is received while there is no data to be read in the buffer memory of the CPU.

*3 On any of the following conditions, this module determines that transfer has ended.

(1) A short packet including zero-length packet is received

(2) The number of packets equal to the value set with the transaction counter are received.

Reception enabled state

Reading enabled state

(2) Data packet reception when BFRE = 1 (in single buffer mode)

USB bus

FIFO buffer status

Reception enabled state

Reading enabled state

BRDY interrupt

(corresponding

PIPEBRDY bit is

changed)

Reading from the buffer

is enabled*2.

A BRDY interrupt is generated

because the transfer has ended*3.

(3) Packet transmission (in single buffer mode)

USB bus

FIFO buffer status

Transmission enabled state

Writing enabled state

BRDY interrupt

(corresponding

PIPEBRDY bit is

changed)

A BRDY interrupt is generated

because writing to the buffer is enabled.

Packet transmitted by the host Packet transmitted by the peripheral module

*1

*1

*1

Figure 26.3 Timing at which a BRDY Interrupt is Generated