Section 27 Video Display Controller 3

Page 1608 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

27.7.26 Chroma-Key Control Registers (GROPCRKY0_1 and GROPCRKY0_2)

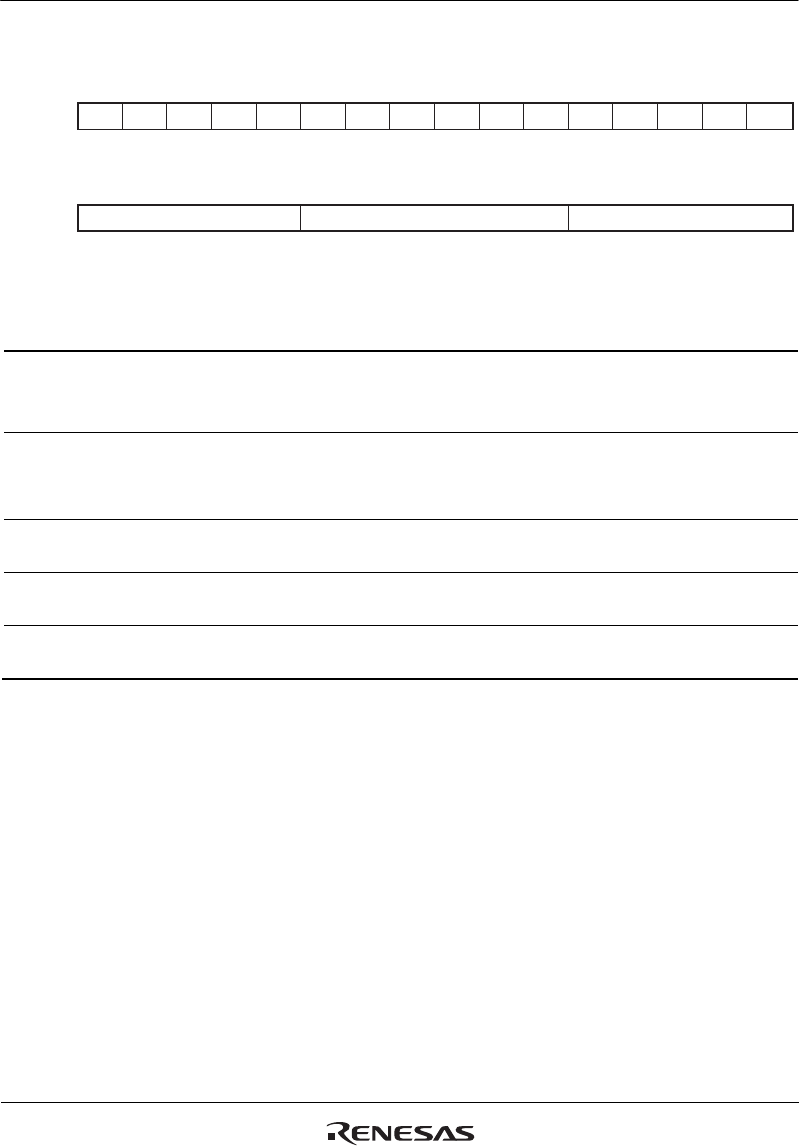

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

RRRRRRRRRRRRRRRR/W

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

---------------CKEN

CROMAKR[4:0] CROMAKG[5:0] CROMAKB[4:0]

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

Bit Bit Name

Initial

Value R/W Description

31 to 17 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

16 CKEN 0 R/W Enables or disables chroma-key processing.

0: Chroma-key processing is disabled.

1: Chroma-key processing is enabled

15 to 11 CROMAKR

[4:0]

00000 R/W These bits specify chroma-key target color R.

10 to 5 CROMAKG

[5:0]

000000 R/W These bits specify chroma-key target color G.

4 to 0 CROMAKB

[4:0]

00000 R/W These bits specify chroma-key target color B.

Note: When the bus format is RGB444, only the CROMAKR[3:0], CROMAKG[3:0], and

CROMAKB[3:0] bits are valid.

When WE =1 in GROPEDPA, the register setting is loaded in the internal circuits in

synchronization with Vsync.

While the chroma-key processing is enabled, if the graphics data values (RGB16 format) of a

pixel all match the CROMAKR[4:0], CROMAKG[5:0], and CROMAKB[4:0] settings, the pixel

color is replaced with the color (RGB16 format) specified in the chroma-key color register

(GROPCRKY1) and processing specified through the ALPHA[7:0] bits is applied.

Chroma-keying thus enables characters or a cursor to be displayed on the lower layer.