Section 26 USB 2.0 Host/Function Module

R01UH0134EJ0400 Rev. 4.00 Page 1517 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

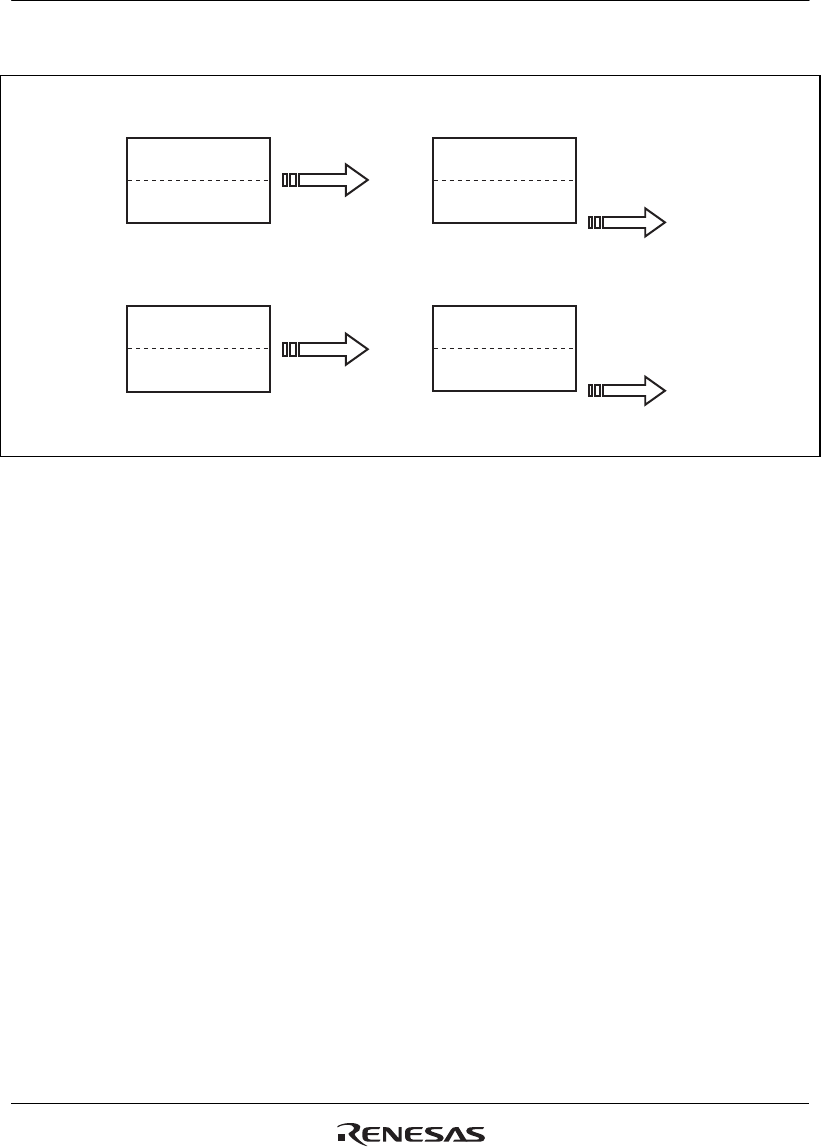

Figure 26.11 shows an example of buffer memory operation for this module.

CNTMD = 0

When packet is received

CNTMD = 1

When packet is received

CNTMD = 0

When packet is sent

CNTMD = 1

When packet is sent

Max Packet Size

Max Packet Size

Max Packet Size

Max Packet Size

Max Packet Size

Max Packet Size

Unused area

Unused area

Interrupt issued

Interrupt issued

Transmission

enabled

Transmission

enabled

Figure 26.11 Example of Buffer Memory Operation

(2) FIFO Port Functions

Table 26.23 shows the settings for the FIFO port functions of this module. In write access, writing

data until the buffer is full (or the maximum packet size for non-continuous transfers)

automatically enables sending of the data. To enable sending of data before the buffer is full (or

before the maximum packet size for non-continuous transfers), the BVAL bit in C/DnFIFOCTR

must be set to end the writing. Also, to send a zero-length packet, the BCLR bit in the same

register must be used to clear the buffer and then the BVAL bit set in order to end the writing.

In read access, reception of new packets is automatically enabled if all of the data has been read.

Data cannot be read when a zero-length packet is being received (DTLN = 0), so the BCLR bit in

the register must be used to release the buffer. The length of the data being received can be

confirmed using the DTLN bit in C/DnFIFOCTR.