Section 26 USB 2.0 Host/Function Module

Page 1380 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

26.3.10 Interrupt Enable Register 0 (INTENB0)

INTENB0 is a register that enables or disables the various interrupts. On detecting the interrupt

corresponding to the bit that has been set to 1, this module generates the USB interrupt.

This module sets 1 to each status bit in INTSTS0 when a detection condition of the corresponding

interrupt source has been satisfied regardless of the set value in INTENB0 (regardless of whether

the interrupt output is enabled or disabled).

While the status bit in INTSTS0 corresponding to the interrupt source indicates 1, this module

generates the USB interrupt when the corresponding interrupt enable bit in INTENB0 is modified

from 0 to 1.

This register is initialized by a power-on reset.

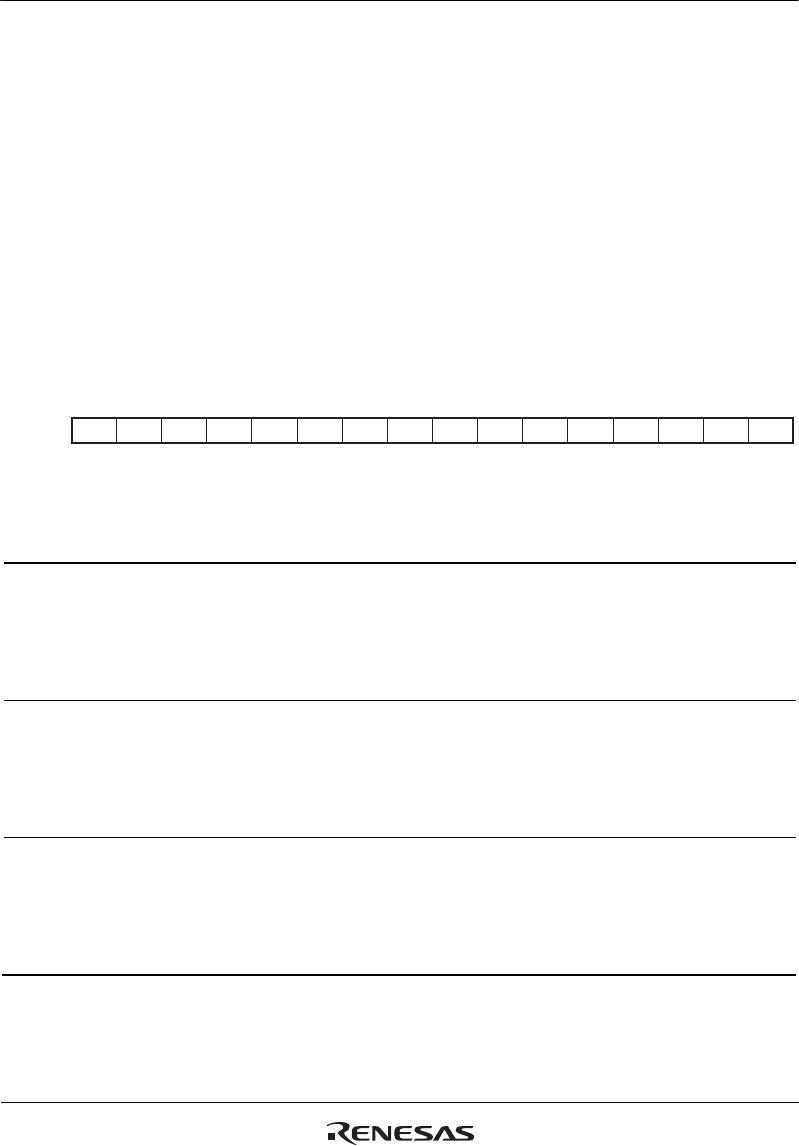

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Bit:

Initial value:

R/W:

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R R R R R R R R

VBSE RSME SOFE DVSE CTRE BEMPE NRDYE BRDYE ————————

Bit Bit Name

Initial

Value R/W Description

15 VBSE 0 R/W VBUS Interrupt Enable

Enables or disables the USB interrupt request when

the VBINT interrupt is detected.

0: Interrupt request disabled

1: Interrupt request enabled

14 RSME 0 R/W Resume Interrupt Enable*

Enables or disables the USB interrupt request when

the RESM interrupt is detected.

0: Interrupt request disabled

1: Interrupt request enabled

13 SOFE 0 R/W Frame Number Update Interrupt Enable

Enables or disables the USB interrupt request when

the SOFR interrupt is detected.

0: Interrupt request disabled

1: Interrupt request enabled