Section 11 Multi-Function Timer Pulse Unit 2

Page 538 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

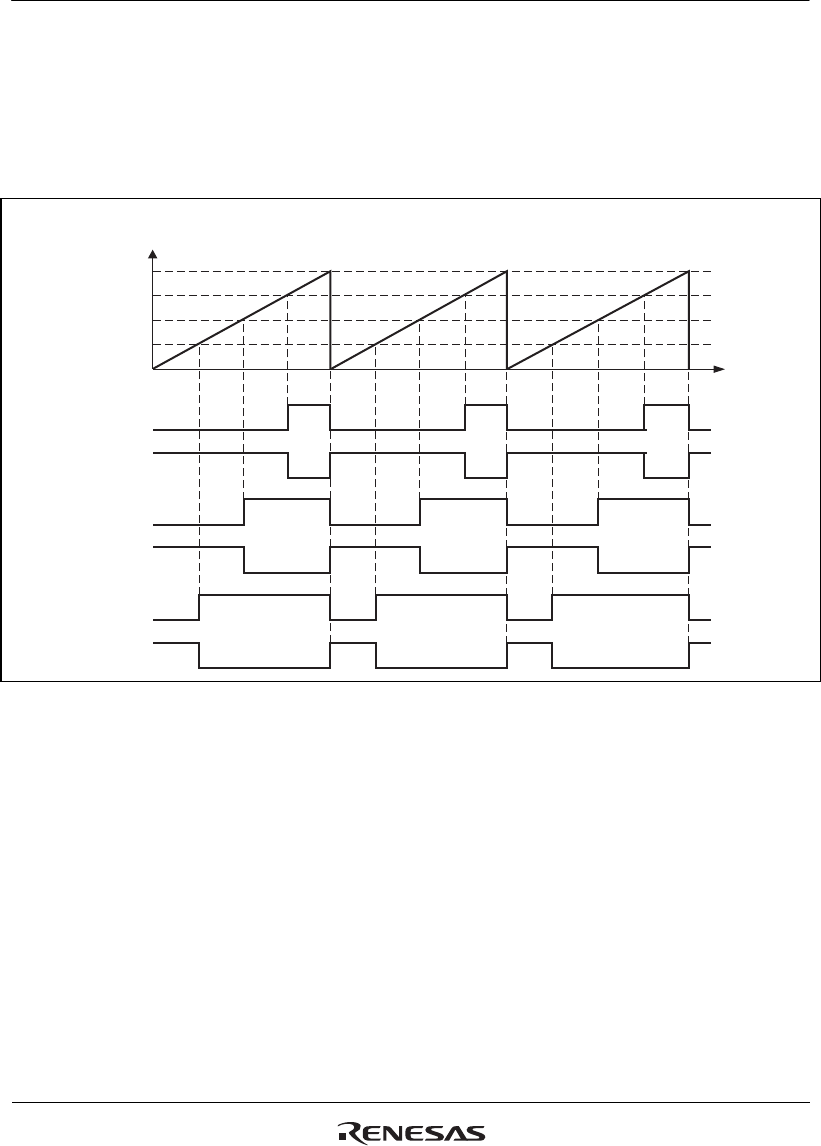

(2) Reset-Synchronized PWM Mode Operation

Figure 11.36 shows an example of operation in the reset-synchronized PWM mode. TCNT_3 and

TCNT_4 operate as upcounters. The counter is cleared when a TCNT_3 and TGRA_3 compare-

match occurs, and then begins incrementing from H'0000. The PWM output pin output toggles

with each occurrence of a TGRB_3, TGRA_4, TGRB_4 compare-match, and upon counter clears.

TGRA_3

TGRB_3

TGRB_4

H'0000

TGRA_4

TIOC3B

TIOC3D

TIOC4A

TIOC4C

TIOC4B

TIOC4D

Time

TCNT_3 and TCNT_4

values

Figure 11.36 Reset-Synchronized PWM Mode Operation Example

(When TOCR’s OLSN = 1 and OLSP = 1)