Section 2 CPU

Page 86 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

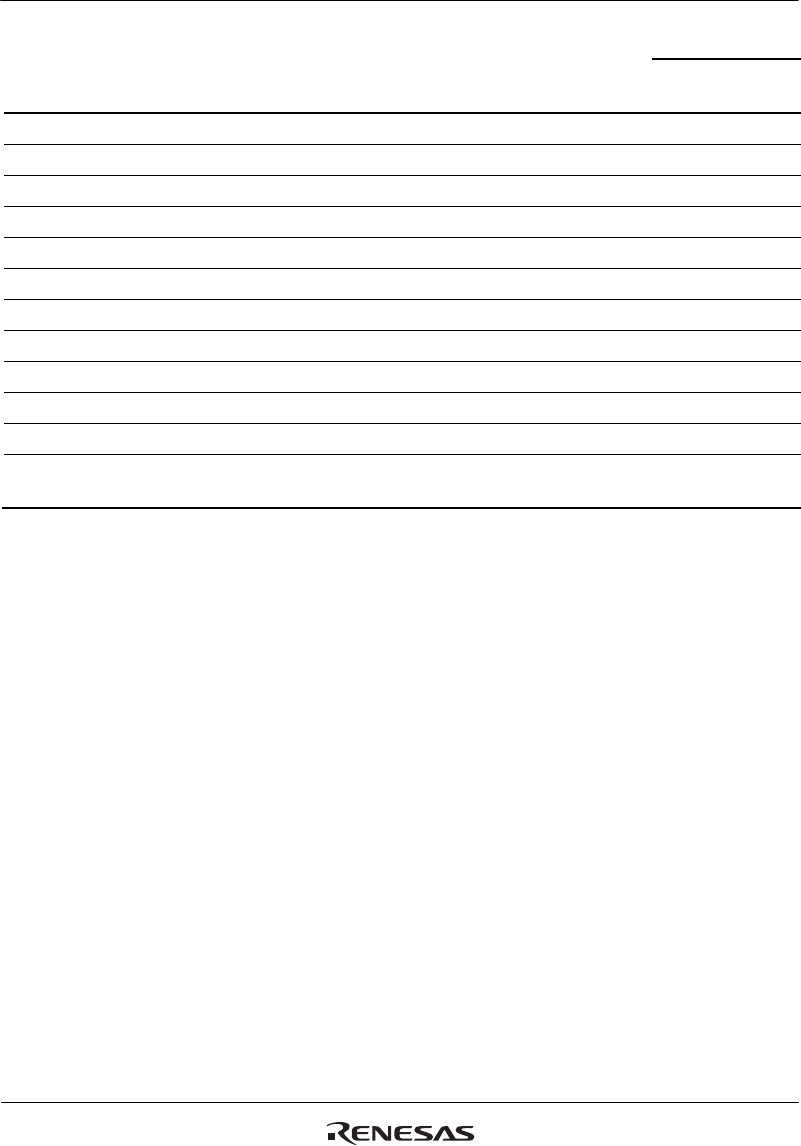

Instruction Instruction Code Operation

Execu-

tion

Cycles T Bit

Compatibility

SH2,

SH2E SH4 SH-2A

STC GBR,Rn 0000nnnn00010010 GBR Rn 1 Yes Yes Yes

STC VBR,Rn 0000nnnn00100010 VBR Rn 1 Yes Yes Yes

STC.L SR,@-Rn 0100nnnn00000011 Rn-4 Rn, SR (Rn) 2 Yes Yes Yes

STC.L GBR,@-Rn 0100nnnn00010011 Rn-4 Rn, GBR (Rn) 1 Yes Yes Yes

STC.L VBR,@-Rn 0100nnnn00100011 Rn-4 Rn, VBR (Rn) 1 Yes Yes Yes

STS MACH,Rn 0000nnnn00001010 MACH Rn 1 Yes Yes Yes

STS MACL,Rn 0000nnnn00011010 MACL Rn 1 Yes Yes Yes

STS PR,Rn 0000nnnn00101010 PR Rn 1 Yes Yes Yes

STS.L MACH,@-Rn 0100nnnn00000010 Rn-4 Rn, MACH (Rn) 1 Yes Yes Yes

STS.L MACL,@-Rn 0100nnnn00010010 Rn-4 Rn, MACL (Rn) 1 Yes Yes Yes

STS.L PR,@-Rn 0100nnnn00100010 Rn-4 Rn, PR (Rn) 1 Yes Yes Yes

TRAPA #imm 11000011iiiiiiii PC/SR stack area,

(imm 4 + VBR) PC

5 Yes Yes Yes

Notes: 1. Instruction execution cycles: The execution cycles shown in the table are minimums. In

practice, the number of instruction execution states in cases such as the following:

a. When there is a conflict between an instruction fetch and a data access

b. When the destination register of a load instruction (memory register) is the same

as the register used by the next instruction.

* In the event of bank overflow, the number of cycles is 19.