Section 27 Video Display Controller 3

Page 1616 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

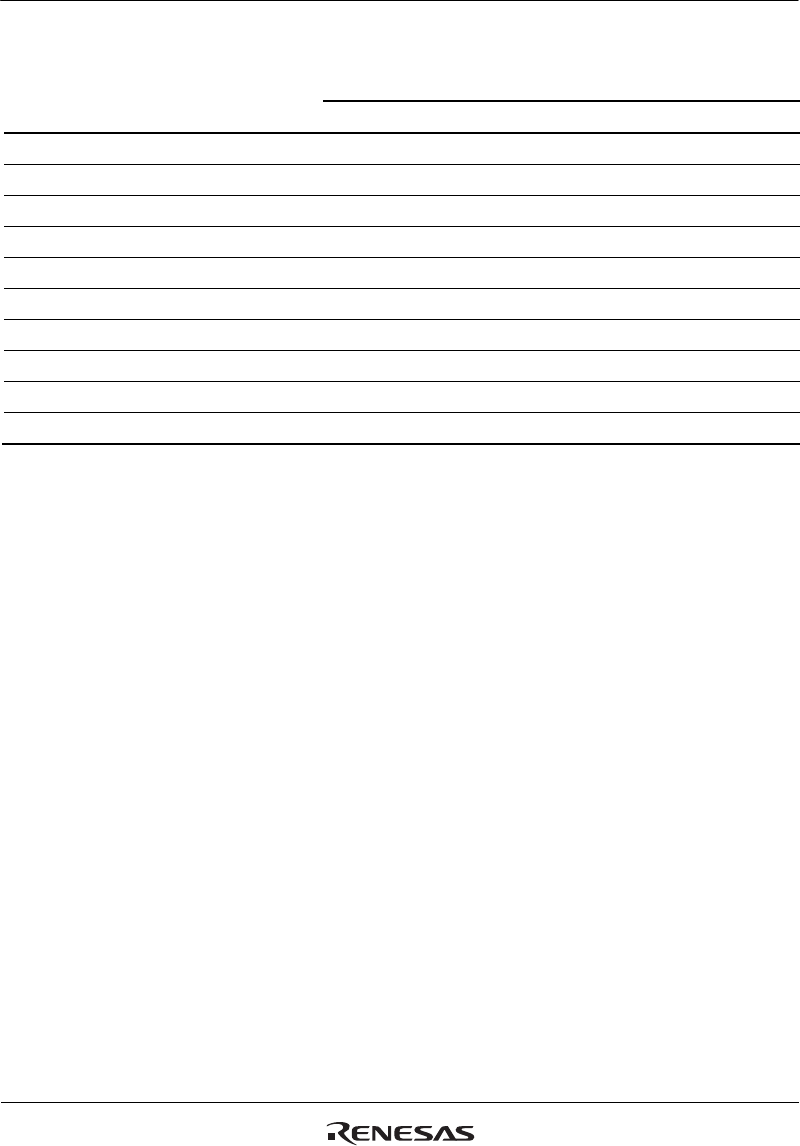

Table 27.14 Input/Output Clock Frequency and Division Ratio

DCDR[5:0]

Clock Frequency

Division Ratio

Input/Output Clock Frequency (MHz)

36.000 48.000*

2

72.000*

2

000001*

1

1/1 36.000 48.000 72.000

000010 1/2 18.000 24.000 36.000

000011 1/3 12.000 16.000 24.000

000100 1/4 9.000 12.000 18.000

000110 1/6 6.000 8.000 12.000

001000 1/8 4.500 6.000 9.000

001100 1/12 3.000 4.000 6.000

010000 1/16 2.250 3.000 4.500

011000 1/24 1.500 2.000 3.000

100000 1/32 1.125 1.500 2.250

Notes: 1. Setting prohibited when the bus clock (B) is selected for the source of the panel clock.

2. When the bus clock (B) is selected for the source of the panel clock.