2-6

iAPX

432

Interface

Processor

Architecture

Reference

Manual

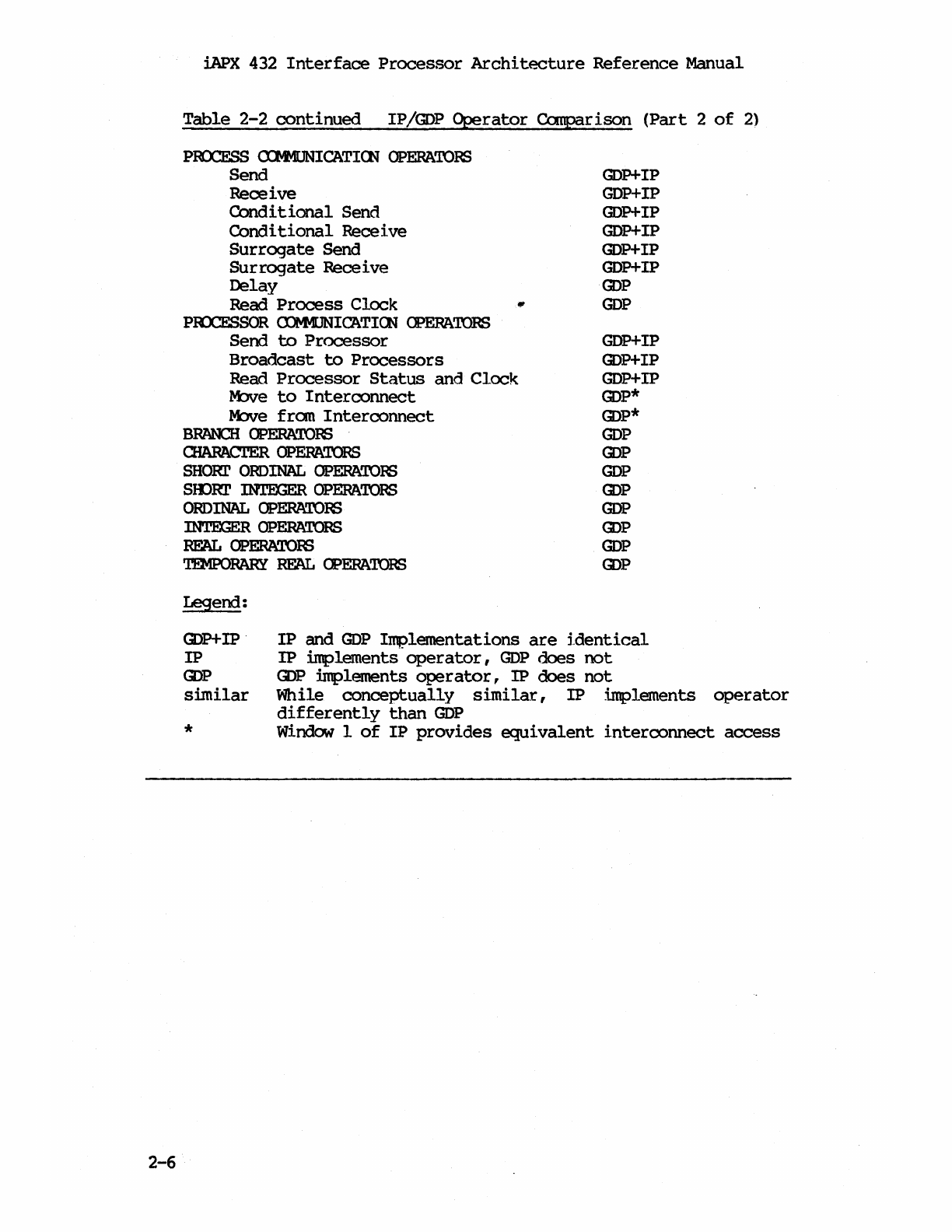

Table

2-2

continued

IP/GOP

Operator

Canparison

(Part

2

of

2)

ProcESS

Cl:H1UNICATICN

OPERA'IORS

Send

Receive

Conditional

Send

Conditional

Receive

Surrogate

Send

Surrogate

Receive

Delay

Read

Process

Clock fII

PR)CESSOR

(X)[\MJNICATIGl

OPERATORS

Send

to

Processor

Broadcast

to

Processors

Read

Processor

Status

and

Clock

MOve

to

Interconnect

MJve

fran

Interconnect

BRANCH

OPERA'IDRS

CHARAcrER

OPERATORS

SHORI'

ORDINAL

OPERATOR)

SIDRr

INT.EX;ER

OPERA'IORS

ORDINAL

OPERATORS

JNTEX;ER

OPERATORS

RFAL

OPERATOR)

'l'ENPORARY

RFAL

CPERATORS

Legend:

GDP+IP

GDP+IP

GDP+IP

GOP+IP

GDP+IP

GOP+IP

GOP

GOP

GOP+IP

GOP+IP

GOP+IP

GOP*

GOP*

GOP

GOP

GOP

GOP

GOP

GOP

GOP

GOP

GOP+IP

.

IP

IP

and

GOP

Implementations

are

i.dentical

IP

implements'·

operator,

GOP

does

not

GOP

similar

*

GOP

implements

operator,

IP

does

not

While

conceptually

similar,

IP

implements

operator

differently

than

GOP

Window

1

of

IP

provides

equivalent

interconnect

access