iAPx

432

Interface

Processor

Architecture

Reference

Manual

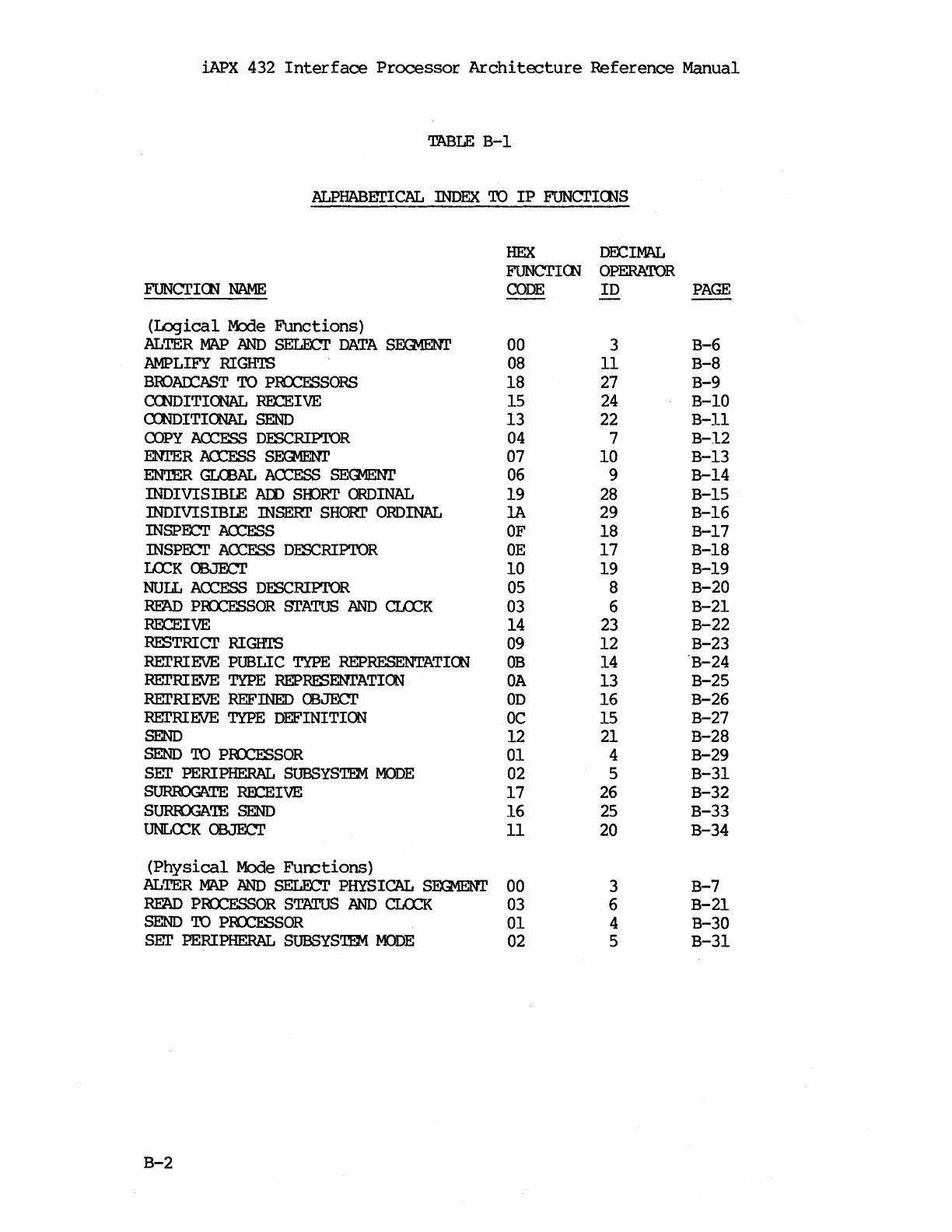

TABLE

B-1

ALPHABEl'ICAL

INDEX

TO

IP

FUNcrICNS

HEX

DECIMAL

FUNCTICN

OPERATOR

FUNcrICN

NAME

CODE

ID

PAGE

(Logical

Mode

Functions)

ALTER

MAP

AND

SEI..:OCT

DATA

SEG1ENT

00

3

B-6

AMPLIFY

RIGHTS

08

11

B-8

BIDAOCAST

TO

P~SORS

18

27

B-9

CCNDITIOOAL ROCEIVE

15

24

B-I0

roIDITICNAL

SEND

13

22

B-11

COpy ACCESS DESCRIPTOR

04

7

B-12

ENrER

ACO:SS SEG1ENr

07

10

B-13

ENTER

GLCBAL

ACCESS

SEGmNr

06

9

B-14

INDIVISmIE

AID

SIDRT ORDINAL

19

28

B-15

INDIVISIBLE

INSERr

SHORr ORDINAL

lA

29

B-16

INSPOCT ACO:SS

OF

18

B-17

INSPECr

AOCESS DESCRIPTOR

OE

17

B-18

LOCK

OBJECT

10 19

B-19

NULL

AOCESS DESCRIPTOR

05

8

B-20

READ

P~SOR

srATUS

AND

CLCCK

03

6

B-21

ROCEIVE

14

23

B-22

RESTRIcr

RIGffi'S

09

12

B-23

REI'RIEVE PUBLIC TYPE REPRESENTATICN

OB

14

B-24

REI'RIRVE TYPE REPRESENI'ATICN

OA

13

B-25

REI'RIEVE REFINED

(]3JECr

OD

16

B-26

REI'RIRVE TYPE DEFINITION

OC

15

B-27

SEND

12

21

B-28

SEND

TO

P~SOR

01

4

B-29

SEl'

PERIPHERAL

SUBSYSTEM

MODE

02

5

B-31

SURROGM'E

ROCElVE

17

26

B-32

SURRJGAm

SEND

16

25

B-33

UNLOCK

OBJECT

11

20

B-34

(Physical

Mode

Fuoctions)

ALTER

MAP

AND

SEI..:OCT

PHYSICAL SEG1ENT

00

3

B-7

READ

PROCESSOR

STATUS

AND

CLOCK

03

6

B-21

SEND

TO

P~SOR

01

4

B-30

SEI'

PERIPHERAL

SUBSYSTEM

MODE

02

5

B-31

B-2