DM9161B

10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver

Final 38

Version: DM9161B-12-DS-F01

January 31, 2008

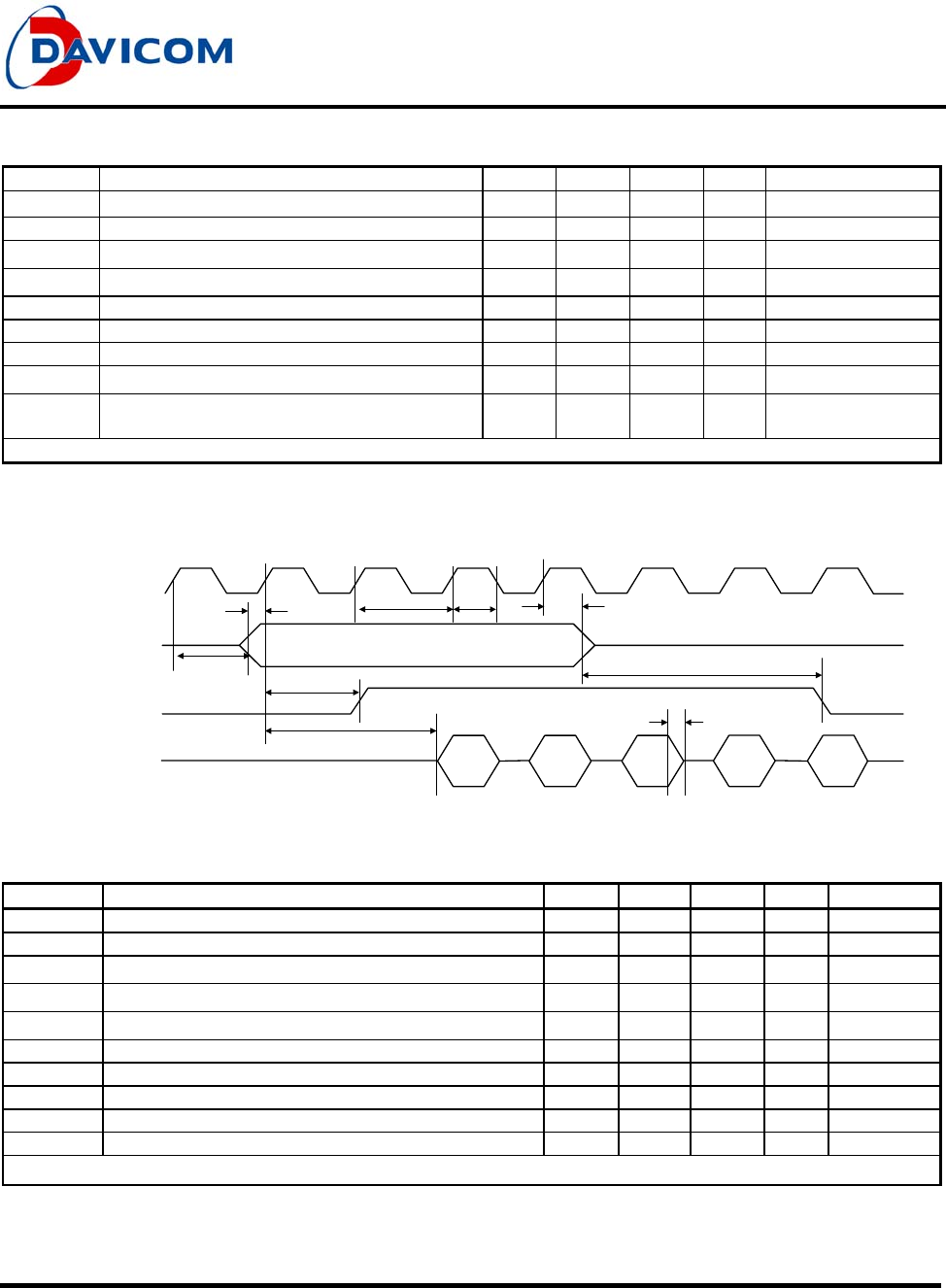

9.4.7 100BASE-TX Transmit Timing Parameters

Symbol Parameter Min. Typ.

Max. Unit Conditions

tTXc TXCLK Cycle Time 39.998 40 40.002 ns 50ppm

tTXh, tTXl TXCLK High/Low Time 16 20 24 ns

tTX

s

TXD [0:3], TXEN, TXER Setup To TXCLK High 12 - - ns

tTX

h

TXD [0:3], TXEN, TXER Hold From TXCLK High 0 - - ns

tTXOD TXCLK to Output Delay 25 ns

t1 TXEN Sampled To CRS Asserted - 4 - BT

t2 TXEN Sampled To CRS De-asserted - 4 - BT

tTX

pd

TXEN Sampled To TX+/- Out (Tx Latency) - 8 - BT

tTX

r/f

100TX Driver Rise/Fall Time 3 4 5 ns 90% To 10%, Into

100ohm Differential

Note 1. Typical values are at 25℃and are for design aid only; not guaranteed and not subject to production testing.

9.4.8 100BASE-TX Transmit Timing Diagram

TXCLK

t

TX

h

t

2

t

TX

S

t

1

t

TX

pd

t

TX

r/f

TXD [0:3],

TXEN, TXER

CRS

100TX+/-

tTXc tTXh

tTXOD

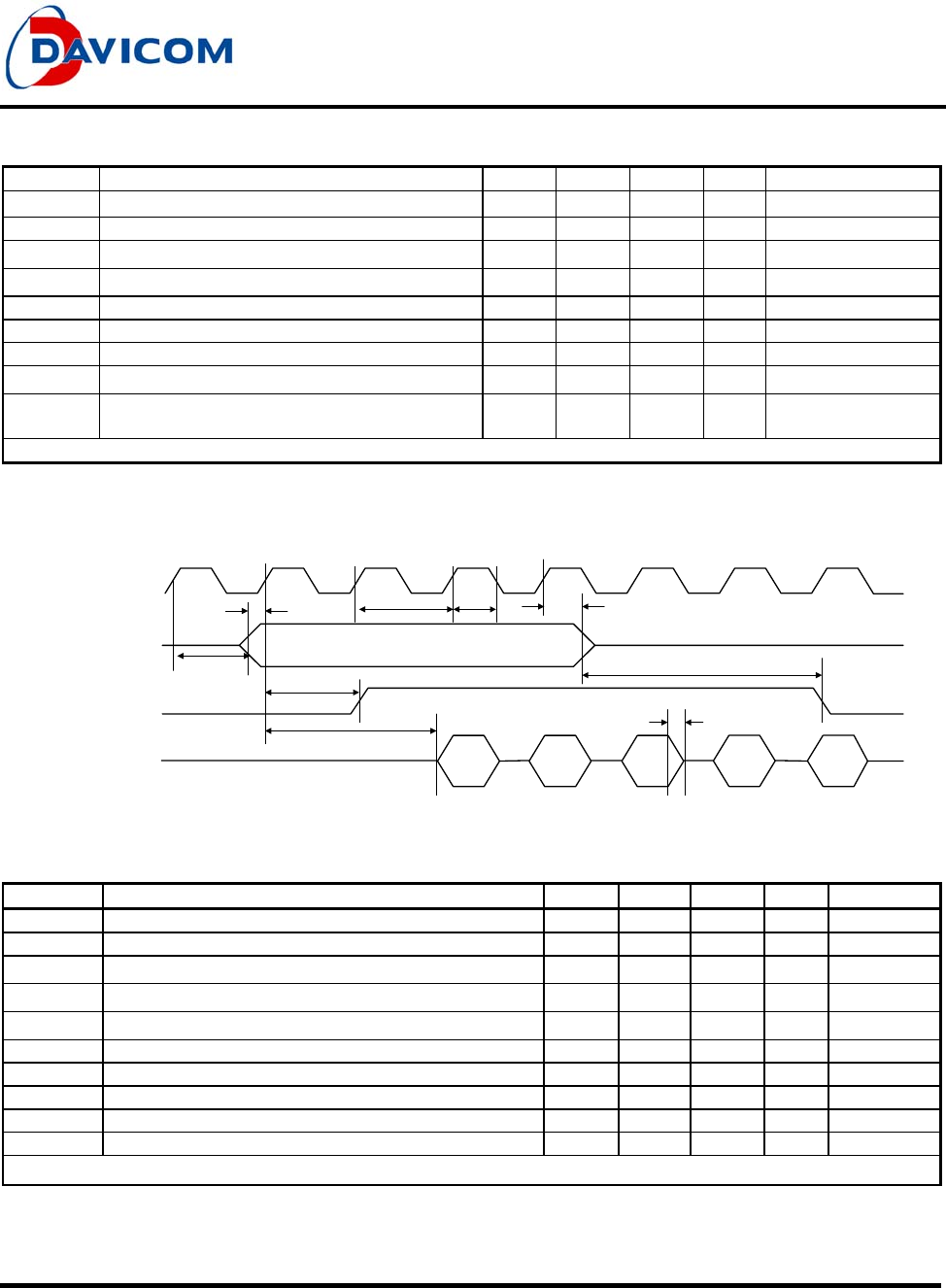

9.4.9 100BASE-TX Receive Timing Parameters

Symbol Parameter Min. Typ.

Max. Unit Conditions

tRXc RXCLK Cycle Time 39.998 40 40.002 50ppm

TRXh, tRXl RXCLK High/Low Time 16 20 24

tRX

s

RXD [0:3], RXDV, RXER Setup To RXCLK High 10 - - ns

tRX

h

RXD [0:3], RXDV, RXER Hold From RXCLK High 10 - - ns

tRX

pd

RX+/- In To RXD [0:3] Out (Rx Latency) - 15 - BT

t1 CRS Asserted To RXD [0:3], RXDV, RXER - 4 - BT

t2 CRS De-asserted To RXD [0:3], RXDV, RXER - 0 - BT

t3 RX+/- In To CRS Asserted 10 - 14 BT

t4 RX+/- Quiet To CRS De-asserted 14 - 18 BT

t5 RX+/- In To COL De-Asserted 14 - 18 BT

1

. Typical values are at 25℃and are for design aid only; not guaranteed and not subject to production testing.