- 39 -

INFORMATION OF ICS

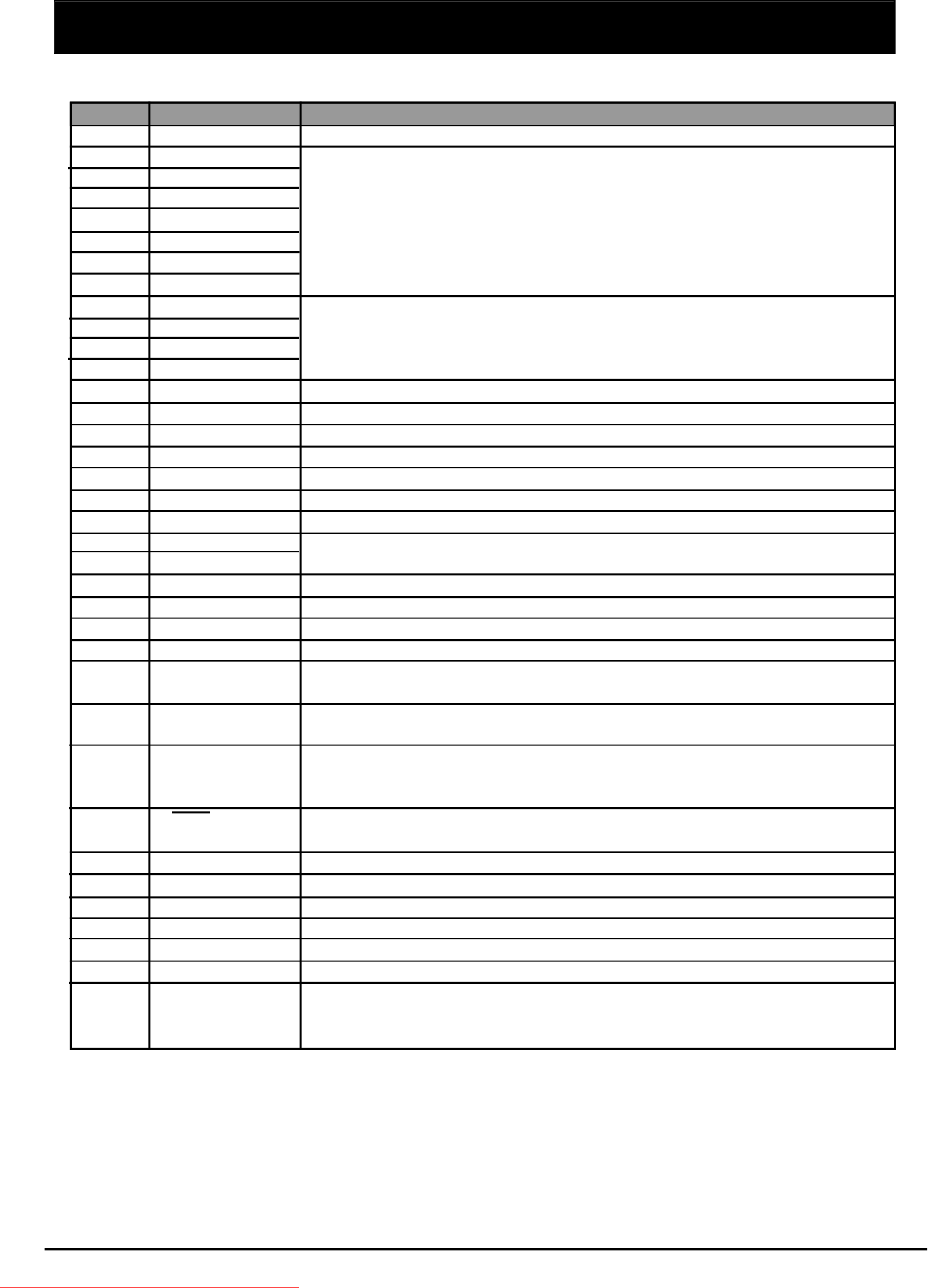

IC SAA5264PS/M3/0104 SDIP52

Pin No. Pin Name Description

1 PWM Output for 14-bit high precision Pulse Width Modulator(PWM)

2 PWM0 Output for 6-bit PWMs 0 to 6

3 PWM1

4 PWM2

5 PWM3

6 PWM4

7 PWM5

8 PWM6

9 ADC0 Inputs for the software Analog-to-Digital-Converter(ADC) facility

10 ADC1

11 ADC2

12 ADC3

13 VSCC Core ground

14 SCL(NVRAM) I

2

C-bus Serial Clock input to Non-Volatile RAM

15 SDA(NVRAM) I

2

C-bus Serial Data input/output (Non-Volatile RAM)

16 Input/output for general use

17 Input/output for general use

18 Input/output for general use

19 8mA current sinking capability for direct drive of Light Emitting

20 Diodes (LEDs)

21 Input/output for general use

22 VSSA Analog ground

23 CVBS0 Composite Video Baseband Signal(CVBS) input; a positive-going

24 CVBS1 1 V (peak-to peak) input is required; connected via a 100 nF capacitor

25 SYNC_FILTER Sync-pulse-filter input for CVBS; this pin should be connected to VSSA

via a 100nF capacitor

26 IREF Reference current input for analog circuits; for correct operation a

24kΩ resistor should be connected to VSSA

27 FRAME Frame de-interlace output synchronized with the VSYNC pulse to

produce a non-interlaced display by adjustment of the vertical

deflection circuits

28 TEST Not avallable; connect this pin to VSSA

29 COR Contrast reduction:open-drain, active LOW output which allows selective

contrast reduction of the TV picture to enhance a mixed mode display

30 PWM7 Output for 6-bit PWM7

31 VDDA Analog supply voltage (3.3V)

32 B Blue colour information pixel rate output

33 G Green colour information pixel rate output

34 R Red colour information pixel rate output

35 VDS Video/data switch push-pull output for pixel rate fast blanking

36 HSYNC Horizontal sync pulse input: Schmitt triggered for a Transistor Transistor

Lever(TTL) version; the polarity of this pulse is programmable by

register bit TXT1.H POLARITY

Downloaded From TV-Manual.com Manuals